台积电的最新技术布局

据台积电在最新年报中披露,2021年,台积公司为535个客户生产1万2,302种不同的产品。其应用范围涵括整个电子应用产业,包括于个人计算机与其周边产品、信息应用产品、有线与无线通讯系统产品、高效能运算服务器与数据中心、汽车与工业用设备,以及包括数位电视、游戏机、数字相机等消费性电子、人工智能物联网及穿戴式设备,与其他许多产品与应用。

能够获得这样的成就,与公司持之以恒的技术投入有重要的关系。按照台积电所说,公司去年全年研发总支出占营收之7.9%,此一研发投资规模相当于或超越了许多其他高科技领导公司的规模。这也帮助公司在多个领域进行了布局。从财报可以看到,除了发展互补金属氧化物半导体(CMOS)逻辑技术,台积公司广泛的对其他半导体技术进行研发,以提供客户行动系统单芯片(SoC)及其他应用所需的功能。

具体而言,台积电在2021年完成的技术包括以下这些:

1、通过第五代(Gen-5)CoWoS的验证,硅中介层面积高达2,500平方毫米,可容纳至少二个系统单晶逻辑芯片和八个高频宽存储器(HBM)小芯片堆栈;

2、成功验证第七代整合型扇出层叠封装技术(InFO-PoP), 可支援具备增强散热性的行动应用;

3、开始生产第三代整合型扇出暨基板封装技术(InFO-oS Gen-3),提供更多的芯片分割及整合,拥有更大的封装尺寸和更高的频宽;

4、扩大90纳米、55纳米、40纳米以及22纳米技术的十二吋BCD技术组合,支援不同整合度的各种快速成长的行动电源管理芯片应用;

5、维持28纳米嵌入式快闪存储器的稳定高良率且达成技术验证,支援消费电子级与第一级车用电子技术应用;

6、40纳米电阻式随机存取存储器(RRAM)进入量产,28纳米和22纳米准备量产,以作为价格敏感的物联网市场的低成本解决方案;

7、增加22纳米磁性随机存取存储器(MRAM)生产率,于2021年完成技术验证,以支援下一世代嵌入式存储器MCU、车用电子元件、物联网,以及人工智能应用;

8、在四相侦测(Quad Phase Detection, QPD)CMOS传感器结构达成13%的画素尺寸微缩,支援行动影像市场。

而截止2021年,台积电已经开发或已提供的制程技术包括:

逻辑制程技术

3纳米鳍式场效晶体管制程(Fin Field-Effect Transistor, FinFET)(N3)技术开发依照计划进行并有很好的进展,并预计于2022下半年开始量产。

N3增强型(N3E)技术系N3技术的强化版,技术开发依照计划进行并有很好的进展。N3E技术将持续针对行动通讯与高效能运算应用提供领先业界的优势,量产时间预计在N3量产后一年进行。

4纳米FinFET(N4)技术为5纳米FinFET(N5)技术的强化版,已于2021年为客户产品试产,并预计于2022年量产。

4纳米FinFET强效版(4nm FinFET Plus, N4P)技术开发依照计划进行并有很好的进展,并预计于2022年试产。

N4X制程技术于2021年推出。此一技术系台积公司针对高效能运算产品所量身打造,在台积公司5纳米系列制程技术中,展现极致效能与最高运作时脉,预计于2023年上半年试产。

5纳米FinFET强效版(N5P)技术为N5技术的效能强化版技术,已于2021年量产。

6纳米FinFET(N6)技术于2020年量产,并于2021年广泛应用于手机、高效能运算,以及消费性电子产品。

7纳米FinFET(N7)及7纳米FinFET强效版(N7+)技术已为客户量产5G及高效能运算产品多年,并于2021年开始为客户量产消费性电子与车用产品。

12纳米FinFET精简型强效版(12nm FinFET Compact Plus, 12FFC+)技术于2021年第一季量产。

奠基于12FFC+的技术及硅智财生态系统的N12eTM技术,于2021年推出新的极低漏电的极高阀值元件(Extreme High Threshold Voltage, eHVT)。

22纳米超低漏电(Ultra-Low Leakage, ULL)(22ULL)技术于2021年推出新的强化版低漏电及具有成本效益的元件,进一步强化22ULL技术平台,以支援客户更广泛的产品应用。

特殊制程技术

5纳米车用基础硅智财(Foundation IP)开发依照计划进行并有很好的进展,并预计于2022年通过AEC-Q100 Grade-2验证。

N6射频(Radio Frequency, RF)(N6 RF)技术于2021年开发完成,客户产品投片预计于2022年开始。

16纳米FinFET精简型(16nm FinFET Compact, 16FFC)射频技术于2021接获多个客户产品的投片。

22ULL RF技术于2021年开始量产,涵盖消费性电子与车用产品等应用。

22ULL嵌入式RRAM技术是台积公司第二代RRAM解决方案,具备成本和可靠性的平衡。2021年已有多个客户采用此一技术完成产品验证并准备生产。

22ULL嵌入式MRAM技术硅智财于2021年完成超过100万次的循环操作耐久性和回流焊接能力的验证。此一技术展现了汽车AEC-Q100 Grade-1能力,并已为客户量产穿戴式产品多年。

28纳米ULL嵌入式快闪存储器制程(eFlash)已通过AEC-Q100 Grade-1可靠性认证技术,于2021年完成安全产品验证,并将为客户量产。

十二吋晶圆40纳米绝缘层上覆硅(Silicon On Insulator, SOI)(N40SOI)技术提供领先业界的竞争优势,于2021年接获多家客户产品投片,并预计2022年开始量产。

十二吋90纳米双载子-互补式金氧半导体-扩散金属氧化半导体强效版(Bipolar-CMOS-DMOS Plus, BCD Plus)技术于2021年通过验证。台积公司也于同年协助客户完成新的设计定案,并采用此一技术开始量产。

第一代硅基板氮化镓(Gallium Nitride on Silicon)技术平台于2021年完成进一步强化,以支援客户多元的市场应用。第二代硅基板氮化镓技术平台开发中,并预计于2022年完成开发。

持续精进互补式金氧半导体影像传感器(CMOS Image Sensor, CIS)技术,因应智慧手机对先进影像传感器的强劲需求。2021年,台积公司协助客户将世界最小画素的产品导入市场。

台积公司成功于2021年采用压电(Piezoelectric)微机电(Micro Electro-mechanical Systems, MEMS) (Piezoelectric MEMS)技术协助客户推出首款微机电单芯片扬声器。

具体而言,台积电的特殊技术和应用覆盖如下所示:

(1)混合讯号/射频

随着第五代行动通讯技术(5G)毫米波时代的到来,台积公司已经提供了许多利用射频设计-技术协同优化(DTCO)具有竞争力的技术解决方案。2021年,台积公司持续提供6纳米射频技术支援5G收发器设计,也提供40纳米特殊制程支援在6GHz以下设计的5G射频前端模块(FEM),以及提供28纳米高效能精简型强效版(HPC+)制程支援5G毫米波FEM设计。

(2)电源IC/双极-互补金属氧化半导体-双重扩散金属氧化半导体(BCD)

2021年,台积公司扩大其十二吋BCD技术的制程组合,涵盖90纳米、55纳米、40纳米以及22纳米,以因应快速成长的行动电源管理芯片应用,例如专用的5伏电源开关,以因应锂电池驱动的功耗成长需求。90纳米BCD技术顺利进入量产,支援5伏到35伏的广泛应用,40纳米BCD 20/24伏技术也开始量产,具备超低功耗基准与整合式可变电阻存储器模块。公司将持续开发28伏及5-16伏高压元件以涵盖更多的电源管理芯片应用。

(3)微机电系统

2021年,台积公司完成压电微机电技术的验证,以生产具备高音质及快速响应的微机电扬声器。未来计划包含开发下一世代高敏感度压电麦克风、十二吋晶圆微机电光学影像稳定(Optical Image Stabilization, OIS)系统、医疗用单芯片超音波传感器,以及车用微机电应用。

(4)氮化镓半导体

2021年,台积公司第一代650伏氮化镓增强型高电子移动率晶体管(E-HEMT)完成验证,进入全产能量产,市场已推出超过130款充电器。公司持续扩充产能以满足客户的需求。第二代650伏和100伏E-HEMT之质量因素(FOM)皆较第一代提升50%,预计于2022年投入生产。100伏空乏型氮化镓高电子移动率晶体管(D-HEMT)已完成元件开发,预计于2022投入生产。此外,台积公司也开始开发第三代650伏增强型高电子移动率晶体管,预计于2025年推出。

(5)互补式金属氧化物半导体(CMOS)影像传感器

2021年,台积公司在互补式金属氧化物半导体影像传感器技术获得数项技术进展,包括:

(a)在崭新的四相侦测(Quad Phase Detection, QPD)传感器结构上画素尺寸微缩13%,可支援行动影像感测市场;

(b)电容在双重转换增益(Dual Conversion Gain)与横向溢出集合电容(Lateral Overflow Integrating Capacitor)影像传感器上实现画素内嵌式三维高密度金属-介电质-金属(MiM),支援高动态范围机械视觉与安全相机的应用;

(c)量产新世代车用影像传感器,具有比前几代产品高25dB的动态范围与低三倍的暗态电流,与可应用于自动驾驶辅助系统之能力。

(6)嵌入式快闪存储器/新兴存储器

2921年,台积公司在嵌入式非挥发性存储器(Non-volatile Memory, NVM)技术领域达成数项重要的里程碑。在28纳米制程方面,支援高效能行动运算与高效能低漏电制程平台的嵌入式快闪存储器开发维持稳定的高良率,并已通过消费性电子级与第一级车用电子技术验证,预计于2023年完成最高规格第零级车用电子技术与产品验证。台积公司亦提供电阻式随机存取存储器技术,作为低成本嵌入式非挥发性存储器解决方案,支援对价格敏感的物联网市场。40纳米进入量产,而28纳米和22纳米已准备量产。

台积公司也在嵌入式磁性随机存取存储器完成数项重要成就。已量产的22纳米MRAM,透过简化整合制程已成功提高产能,于2021年完成技术验证。支援车用电子应用的16纳米制程亦维持稳定的高良率,预计于2023年完成技术验证。同时,台积公司完成了多功能磁性随机存取存储器之可行性评估,以因应客户在微控制器(MCU)、人工智能,以及虚拟实境(VR)应用上高速及低功耗之要求。

3DFabricTM :台积公司先进封装技术

TSMC-SoICTM(系统整合芯片)三维硅堆栈制程技术中的芯片对晶圆(Chip on Wafer, CoW)技术,成功于2021年在客户产品的静态随机存取存储器(Static Random Access Memory, SRAM)与逻辑芯片的异质整合(Heterogeneous integration)上,展现出优异的电性表现。

CoWoS®-S(Chip on wafer on substrate with silicon interposer)技术于2021年新增了嵌入式深沟槽电容的选择以及扩大硅基板至三倍光罩尺寸,并且完成验证,协助客户在高效能运算产品运用上,能够整合更多的逻辑与高频宽存储器(High Bandwidth Memory)。

CoWoS®-R(Chip on wafer on substrate with redistribution layer interposer)技术于2021年完成技术验证。

用于N 4晶圆覆晶封装的细小间距阵列铜凸块(C u bump)技术于2021年成功进入试产。2021年,台积公司致力于维系与许多世界级研究机构的强力合作关系,包括美国的SRC及比利时的IMEC。公司亦持续扩大与全球顶尖大学的研究合作,达到半导体技术进步和培育未来人才的二大目标。

2021年的研究成果

在财报上,台积电还分享了公司在2021年的研究成果。首先看工艺制造方面:

(1)3纳米制程技术

2021年,台积公司建立平台支援N3技术,支援高效能运算及系统单芯片应用,也开始试产,预计于2022年下半年开始量产。台积公司也开始开发N3E技术,改善了生产制程容许范围,具备更佳的效能与功耗,预计于N3制程量产一年之后量产。

(2)2纳米制程技术

2021年,台积公司进入2纳米制程技术的开发阶段,着重于测试载具之设计与实作、光罩制作,以及硅试产。主要进展在于提升基础制程设定、晶体管与导线效能。

(3)微影技术

2021年,台积公司的研发组织藉由提升晶圆良率达到可靠影像以支援3纳米试产,公司也提升极紫外光(EUV)的应用、降低材料缺陷与增进平坦化的能力以支援2纳米技术的开发。此外,台积公司研发单位致力于减少EUV曝光机光罩缺陷及制程堆栈误差,并降低整体成本。

台积公司的EUV项目在功率输出及稳定性上有持续性的突破,进一步提升生产力,在EUV微影制程控制、光阻材料光罩保护膜,以及光罩生产质量皆有进一步进展,进而提升良率,以达到大量生产所需的要求。未来,公司将持续研究下一世代产品的生产与节能契机,以支援EUV项目达成2050年净零排放的长期目标。

(4)光罩技术

2021年,研发组织聚焦于提升极紫外光光罩在线宽控制和光罩层叠精准度的表现以符合3纳米微影制程的要求。藉由2纳米光罩材料与光罩制程的基础开发,台积公司持续精进极紫外光光罩技术。

来到导线与封装技术整合方面,台积公司将晶圆级芯片到芯片制程之细间距连接技术命名为3DFabricTM,其中包括在互连之前嵌入芯片的整合型扇出(InFO)、将芯片嵌入预制的线路重布层(RDL)上的CoWoS®,以及芯片与芯片直接堆栈的SoIC。

台积公司提供通用晶圆级系统整合(WLSI)技术系列,包括SoIC、晶圆上系统(SoW)和整合基板系统(SoIS),以满足未来运算系统整合微缩的需求。在2021年,公司也取得了下述进展。

1.三维集成电路(3DIC)与系统整合芯片(TSMC-SoICTM)

系统整合芯片(TSMC-SoICTM)是创新的晶圆级前段三维集成电路(3DIC)芯片堆栈平台,具有卓越的接合密度、互连频宽、功耗效率和薄形轮廓,可透过系统级微缩来延续摩尔定律,具有持续性的效能提升和相对应的成本优势。系统整合芯片接下来可以使用传统封装或台积公司崭新的3DFabricTM技术,例如CoWoS®或整合型扇出来做封装,以支援下一世代高效能运算(HPC)、人工智能(AI)和行动应用产品。

目前台积公司的SoIC制程预计于2022年下半年完成初步验证。台积公司将继续追求系统整合芯片技术的微缩,以便与台积公司先进的硅技术保持一致,进一步提高晶体管密度、系统PPA(功耗、性能及面积),以及成本的优势。

2.后芯片(Chip-Last)CoWoS®

含有硅中介层的CoWoS®是针对高端高效能运算与人工智能产品应用的2.5D领先技术。此技术之硅中介层具有次微米级的绕线层和整合电容(integrated Capacitors, iCap),因此可以在上面放置系统单芯片(SoC)和高频宽存储器(HBM)等各种小芯片。第五代CoWoS®的硅中介层面积高达2,500平方毫米,可容纳至少二个SoC逻辑芯片和八个HBM堆栈,已于2021年通过验证。2022年,台积公司的主要重点在于完成验证CoWoS®技术上崭新的第三代HBM。

3.先芯片(Chip-First)整合型扇出(InFO)

2021年,台积公司持续领先业界大量生产第六代整合型扇出层叠封装技术(InFO-PoP Gen-6)以支援行动应用,并生产第三代整合型扇出暨基板封装技术(InFO-oS Gen-3)支援HPC晶粒分割的应用。第七代InFO-PoP也已成功通过验证支援行动应用和增强散热性能。第四代InFO-oS如期完成开发,可提供更多的芯片分割,整合更大的封装尺寸和更高的频宽。

4.先进导线技术

藉由实现领先技术,台积公司先进的导线技术持续协助客户强化竞争力2021年,崭新材料的开发达成了导线电阻与电容的降低,以提升芯片效能。此外,导入创新的导线讯号布线与功耗设计,可提升芯片效能,并同时降低成本。

正在研究的先进技术

元件及材料的创新持续提升先进逻辑技术的效能并降低功耗。2021年,台积公司与二所一流大学合作,成功展示一个在半金属铋(Bi)和半导体的单原子层二维过渡金属二硫族化合物间的创纪录低接触电阻,实现了单原子层二硫化钼二维晶体管的最高导通状态电流密度。

2021年五月,此项突破发表于全球最重要科学期刊之一的《自然》(Nature)。在2021年举行的国际电子元件会议(International Electron Device Meeting, IEDM),台积公司展示了另一项接触技术,进一步提升热稳定性和相对的低接触电阻,该成果亦获得正面的媒体报导。

台积公司持续研究新兴的高密度、非挥发性存储器元件和硬件加速器以支援人工智能和高效能运算应用。台积公司与美国重点大学密切合作,在国际固态电路会议(International Solid-State Circuits Conference, ISSCC)和超大型集成电路技术与电路研讨会(Symposiaon VLSI Technology and Circuits, Symp. VLSI)等高规格会议上发表了数篇关于使用电阻式存储器(RRAM)进行存储器内运算的论文。存储器选择器是实现高密度非挥发性存储器的关键元件。

在2021年的超大型集成电路技术与电路研讨会,台积公司展示了一种高效能无砷的锗碳碲阈值型选择器,具有超过1011次循环的创纪录高耐久性,以及约1.3伏的低阈值电压和约5纳安培的低漏电流。

在2021年的国际电子元件会议,台积公司进一步推出了一种氮掺杂的锗碳碲选择器,能够与后段制程兼容并且具有超低的循环到循环间的阈值电压变动。台积公司也在2021年的超大型集成电路技术与电路研讨会上展示了数种新技术来达成多阶存储器单元(MLC)数据存储,支援神经网络应用,包括多阶存储器单元的相变化存储器(PCM),其保留时间提高了10万倍,同时将推论的准确度下降保持在3%以内。

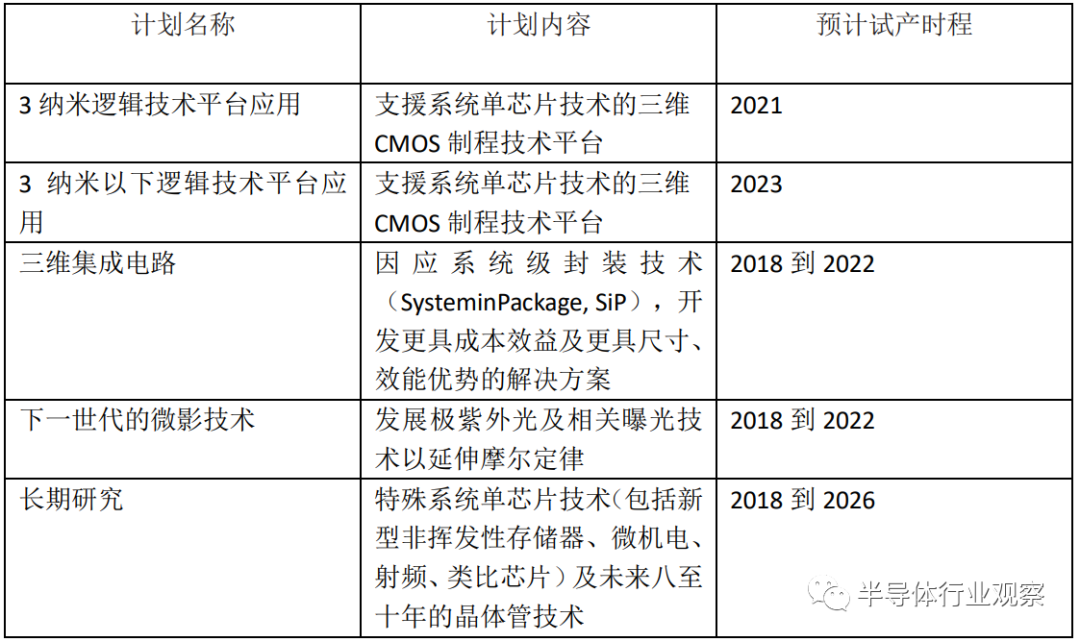

图片说明:以上计划之研发经费约占2022年总研发预算之80%,而总研发预算预估约占2022全年营收的8%。

为保持公司的技术领先地位,台积电表示,公司计划持续大量投资研发。在台积公司3纳米及2纳米先进CMOS逻辑技术持续进展时,台积公司的前瞻研发工作将聚焦于2纳米以

下的技术、三维晶体管、新存储器,以及低电阻导线等领域,为未来技术平台建立坚实的基础。

台积公司的3DIC先进封装研发,正在开发子系统整合的创新,以进一步增强先进的CMOS逻辑应用。公司亦加强聚焦于特殊制程技术,例如射频及三维智能传感器,以支援5G及智能物联网的应用。

先进技术研究部门持续专注于未来八至十年后可能采用的新材料、制程、元件和存储器。台积公司也持续与学术界和产业联盟等外部研究机构合作,旨在为客户尽早了解和采用未来具有成本效益的技术和制造解决方案。

凭借着高度称职及专注的研发团队及其对创新的坚定承诺,台积公司有信心能够透过提供客户有竞争力的半导体技术,推动未来业务的成长和获利。

Newseeders 合作伙伴

Newseeders 合作伙伴